REPORT: How to Make the NSTC a Moonshot Success

Fortune favors the bold! The NSTC needs to take a high-risk, high-reward approach

The National Semiconductor Technology Center (NSTC) has been slower to materialize than manufacturing grants funding under the CHIPS and Science Act of 2022, but this public-private consortium with $11 billion in federal funding behind it has even more potential upside than the $39 billion of manufacturing subsidies.

In a deep-dive report published at the Institute for Progress, Chip Capitols and I highlight market failures that challenge research and investment in the semiconductor industry, and propose an organizational infrastructure that would allow the NSTC to plug these holes as a unique market actor.

To maximize its potential impact, the NSTC needs to shoot for the moon.

It should make high variance bets that could really move the needle on US technological leadership for this century, not just supplement corporate R&D roadmaps.

Be sure to check out the Institute for Progress for the full report!

Executive summary

As the semiconductor industry has specialized in recent years, its ability to organize and cooperate has atrophied. But it faces an increasing number of challenges that will require deep, long-term cooperation. The United States has a chance to ensure an increasingly siloed industry can unite in pursuit of such moonshots on American soil. That chance lies in the National Semiconductor Technology Center (NSTC), funded up to $11 billion by the CHIPS and Science Act of 2022.

The NSTC should not be relegated to the role of a low-risk R&D subsidy, aligned with existing industry agendas. Rather, the consortium should independently tackle hard-to-solve, long-term challenges that no existing entities have the incentive to pursue. In this paper, we highlight market failures that challenge research and investment in the semiconductor industry, and propose an organizational infrastructure that would allow the NSTC to plug these holes as a unique market actor.

The chip industry was born in America, and a sufficiently ambitious NSTC can ensure the next generation of computing technology is continued here. If the NSTC’s ambitious research and investment agendas complement those of private industry, the once-in-a-generation consortium can make a strong argument to Congress for continued funding, becoming an institution with staying power.

Don’t sell the CHIPS moonshot short

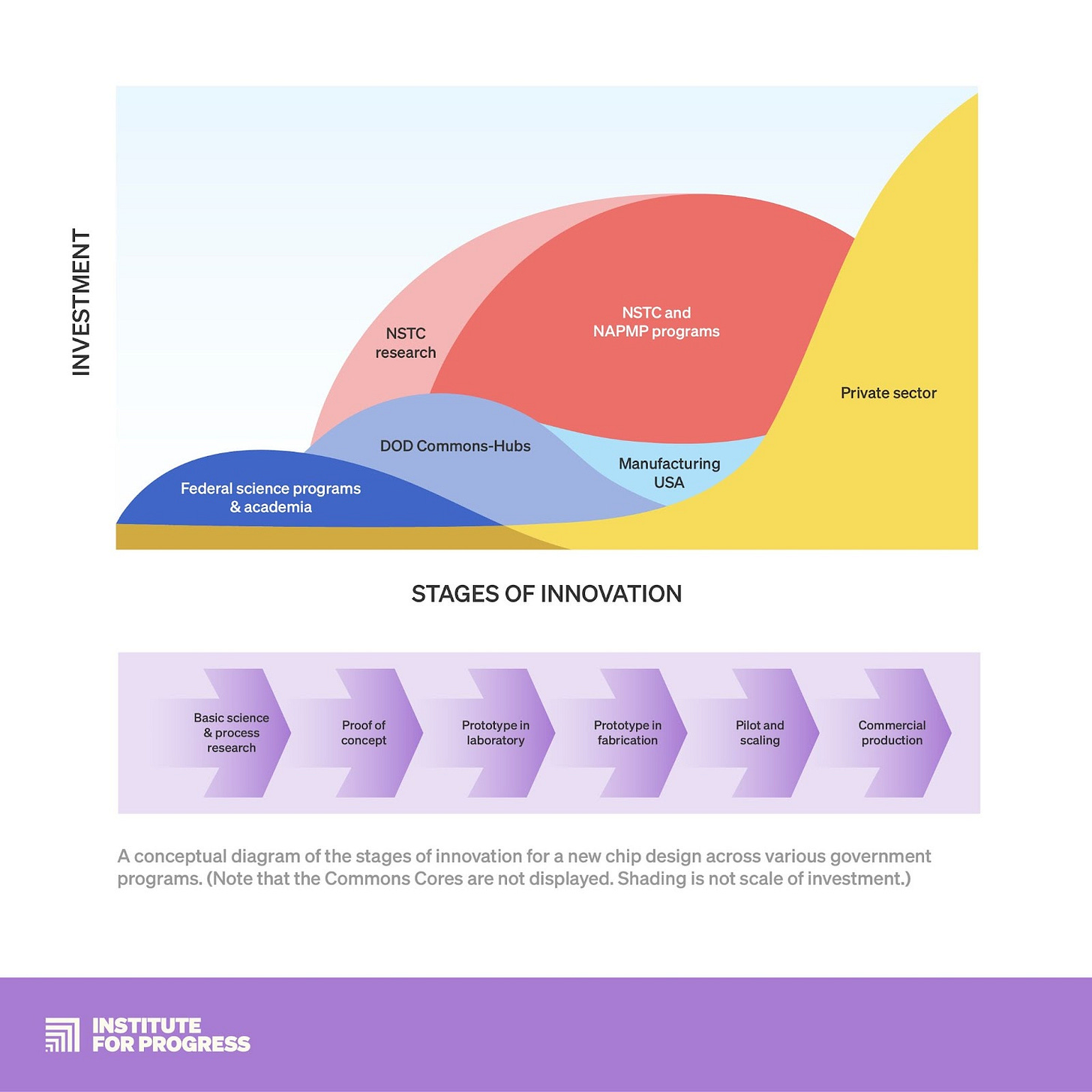

A year and a half after passage of the CHIPS and Science Act of 2022, a nonprofit, Natcast, has finally been established to govern the CHIPS Act’s underappreciated gem: the National Semiconductor Technology Center (NSTC). The CHIPS Act appropriated over $52 billion to revitalize the American semiconductor industry, and its $39 billion reserved for chip manufacturing subsidies received the most attention. More important to America’s long-term technological leadership, however, is another $11 billion set aside to fund a series of research initiatives.

These research initiatives, especially the NSTC, have the potential to turbocharge American innovation. The NSTC consortium is the first American attempt since 1987 to create a public-private partnership for semiconductor technology. Done right, it could lead to paradigm shifts in areas such as computing for machine learning, advanced computing security, and in the environmental sustainability of chipmaking itself.

However, the world is full of research consortia that only incrementally advance technology frontiers. If the NSTC is insufficiently ambitious, it will likely not improve on existing efforts in industry, academia, and foreign consortia. Moreover, it may not produce sufficient value to survive beyond its five years of CHIPS Act funding.

The CHIPS manufacturing grants serve short-term goals: restoring America’s share of global semiconductor manufacturing and securing critical supply chains. The NSTC ought to target a long-term goal: ensure America remains the birthplace of paradigm-shifting technologies. Commerce Department officials should not relegate the NSTC to a low-risk R&D subsidy aligned with existing industry agendas. Rather, the NSTC’s research and investment agendas should pursue paradigm-shifting moonshots.

While Congress laid out clear goals for the manufacturing grants in the CHIPS and Science Act, it left its instructions for the NSTC vague. This ambiguity gives the Commerce Department a unique opportunity to dream ambitiously. Based on dozens of interviews with chip startup founders and venture capitalists,1 this paper articulates a vision for a moonshot-focused NSTC, and proposes the organizational steps for getting there:

Correcting market failures in research and manufacturing

Major players across the chip industry face incentives that create particular shortfalls in their research agendas. Startups struggle to plan for real-world manufacturing environments when developing their early products. Incumbents and startups both insufficiently explore new materials and chemicals, because established supply chains are difficult to disrupt. Siloed firms lack forums for cooperation on research missions that target the computation needs spurred by downstream technological trends, and which no individual semiconductor company is incentivized to solve. In each of these cases, existing market forces lead to a less dynamic chip industry. In some of these cases, the problem isn’t market failures per se; but the market is externalizing risk to things we care about, like supply chain durability and national security. This externalized risk leads actors to invest less than they would in a more robust ecosystem. We propose an NSTC research agenda that addresses these market failures and externalities.

The chip industry’s investment agenda leaves similar gaps that further hamstring these players. Startups benefit from discounted electronic design automation (EDA) tools in their early stages, but often cannot survive the leap to commercialization after these tools expire. Startups operating outside the latest investment trends struggle to attract financing. Lastly, large industry funds, generalist venture capitalists, and institutional investors lack the combination of technical knowledge and financial muscle to organize investing syndicates for promising upstarts.

A research and investment agenda laser-focused on addressing market failures could allow this new American research consortium to orchestrate generational steps forward in computing.

Independent, centralized infrastructure producing shared IP

After explaining our vision for the NSTC’s leadership role in research and investment, we proceed to the how. Our recommendations for the consortium’s IP sharing model, geographic organization, and financial plan will allow the NSTC to solve key market failures.

Natcast leaders should design an NSTC that shares its IP widely in the first decade. As many members as possible should have nonexclusive, royalty-free licenses to IP as the consortium develops. Only after the NSTC’s cross-sectoral research agenda solidifies should the consortium narrow the number of companies with which it shares IP.

The NSTC’s geography should be as centralized as possible. Building facilities around a flagship campus would give Natcast leadership more influence over the consortium’s agenda than it would have with many annexes to existing facilities. This strong leadership will allow the NSTC’s research and investment agenda to avoid industry capture.

Lastly, the NSTC’s financial plan should mimic that of its closest historical peer, Belgium’s Imec. The CHIPS Act gives the consortium an initial five years of relative financial independence, which it should use to build centralized infrastructure. In the second five years, the NSTC should rely more heavily on participation fees for joint efforts, but still use public dollars for infrastructure expansions. After a decade, the NSTC can confidently engage in more direct fee-for-service projects without fear that it will become over-reliant on a small number of private-industry partners.

A unique orientation for the NSTC

The chip industry is rife with grand visions for new paradigms in materials, architectures, and other foundational technologies, but realizing these goals requires tighter cooperation among industry players. In 1987, TSMC’s decision to only fabricate chips that other firms design kicked off the fabless-foundry bifurcation. Today, heterogenous integration further divides the semiconductor world into engineers thinking about fragmentary chiplets and those thinking about the entire chip. Just as the industry has become more siloed, however, downstream trends like autonomous driving demand increasingly seamless communication between sensing and computing systems, technologies developed by different companies in distinct segments of the industry. Each time chipmaking reaches a new level of complexity, it needs new institutional arrangements to orchestrate cooperation among increasingly siloed companies, universities, and financiers.

Imec played such a gathering role in the late-nineties and naughts, when it brought together upstream optics makers, toolmakers, university labs, and downstream chipmakers, and it continues to facilitate cross-industry collaboration toward a limited set of moonshots today. The value-add of gathering places like Imec lies in their ability to incentivize industry players, who would otherwise be unwilling to or incapable of sharing knowledge, to share intellectual property (IP) and engineering talent in pursuit of joint-research projects. For example, the consortium has linked toolmakers, IDMs, and foundries over fifteen years in pursuit of a gallium nitride on silicon (GaN-on-Si) effort that no industry player alone has the incentive structure to coordinate. Imec’s cooperative efforts bore fruit in December 2023, when its GaN-on-Si transistors outperformed industry alternatives.

This alternate development route shows the value of consortia with different incentive structures than private industry. Imec’s diverse research participants and longer time horizons allowed the chipmaking world to bet on two GaN transistor technologies at once, and the best ultimately won out.

Aside from Imec, chipmaking countries across the world boast public-private partnerships seeking to connect subsets of players in pursuit of narrow goals. However, reaching semiconductor technologists’ loftiest moonshots requires gathering competitors, siloed industry segments, and investors in ways that no existing consortium addresses.

This section analyzes how the NSTC could set its research agenda and investment agenda to help correct those market failures.

Correcting market failures in research

The consortium should set its research agenda in line with three high-level goals: proactive design planning for manufacturing, de-risking underinvested areas, and organizing cross-sectoral missions. Such ambitious planning might not immediately yield overwhelming support from all industry players, but the fear of disagreement should not hinder farsighted investment. If the consortium can demonstrate early success, initially skeptical actors may come on board later.

Design for manufacturing

Chip startups often prefer to use laboratory equipment and controlled settings to develop prototypes, as opposed to the less precise tools used in commercial environments. This preference is understandable, as most are pursuing early-stage investment and have limited bandwidth to consider how their prototypes will ultimately reach production scale. However, a venture fund co-founder we interviewed lamented that relying on nearly perfect laboratory conditions delays important design and testing questions. Startups meet messy commercial fabrication environments in the Series B stage, at which point their early funding runs dry. The Series B stage, when startups are too mature for further venture funding but have not yet proven their products with commercial equipment, is referred to as the valley of death.

Insisting that startups participating in the NSTC ecosystem use production-style tools (and providing access to such facilities) will provide early-stage innovators with both the means and the incentive to consider crucial questions about the transition to commercial-scale manufacturing at an earlier stage in their development. The same venture fund co-founder highlighted American SME champion Applied Materials’ long-standing investment in Adesto Technologies as an example of such an approach. Starting from Adesto’s Series A, through the startup’s IPO, Applied Materials (AMAT) provided its own lab space and engineering support to help Adesto prove its designs could scale with commercial equipment. AMAT’s interest in doing so was to improve its own tools and process flows, suggesting that the NSTC could similarly expose startups to commercial environments by incorporating them into its workflow.

An NSTC commitment to “design for manufacturing” in its research agenda could look like Taiwan Semiconductor Manufacturing Company’s (TSMC) enormously successful Design-Technology Co-Optimization (DTCO) methodology. DTCO, and its broader counterpart, System-Technology Co-Optimization (STCO), are methods under which traditionally sequential steps of the chip value chain are undertaken in parallel. In doing so, engineers from different steps of the value chain can more easily learn about and implement changes that lead to efficiency gains for their upstream and downstream colleagues. DTCO notably led to the transition from planar to finFET transistors, and to the development of more accurate chip layout design using lithography and etching tools.

TSMC succinctly described this approach in a 2022 media post:

“TSMC process R&D needs to work with TSMC design R&D on DTCO from day one of next-generation technology definition. Both teams must maintain an open mind as they explore what’s possible in terms of design innovation and process capability. A lot of innovative ideas are proposed at this stage. Some of them could be too aggressive to be realized by current technology. Some of them may look promising initially but turn out to not be so useful.”

Similarly to how TSMC coordinates its various research teams, the NSTC should require all startups it supports for early-stage research to plan for limits of production-stage capabilities. In the worst case, such planning would lead to the early scrapping of unrealistic proposals; in the best case, it would push startups to find creative solutions to circumvent the constraints of commercial environments.

Testing grounds for new materials and new chemicals

The chip industry invests far too little in certain high-potential technology segments. New substrates and new chemicals are examples of how capex barriers and process inertia impede progress.

Semiconductor substrate startups working with wide bandgap (WBG) materials such as silicon carbide (SiC) and gallium nitride (GaN) face a unique set of capex barriers tied to their infrastructure needs. WBG materials are important for computing in contexts like transportation, energy grids, and outer space because they can operate at higher voltages, temperatures, and frequencies than conventional semiconductor materials. Increasing the commercial-level production of WBGs would increase the supply of these materials, as well as the number of facilities that can process them. Such an increase in materials supply and infrastructure would in turn lower the cost of testing for novel WBG chip technology.

Unfortunately, commercial fabs often hesitate to adopt new materials like SiC due to the risk of contaminating their existing production lines, and substrate startups need early adopters to demonstrate the viability of their products. As a result, these startups have limited avenues to test novel substrate technologies. Texas Instrument’s retired X-FAB facility offers SiC and GaN testing lines, and ARPA-E regularly invests in SiC testing; however, these facilities and funds are not nearly enough to support a fertile substrate ecosystem in the U.S. Publicly financed programs in the U.S. devoted to new materials research have in fact declined over the past decade: Founded in 2005 with $20 million in annual public-private funding, the Nanoelectronics Research Initiative (NRI) focused on non-conventional materials and architectures that sought to outperform CMOS over the course of a decade. It was later merged with the STARnet program, which received $50 million in annual funding for six facilities, three of which engaged in beyond-CMOS research. Neither NRI nor STARnet are still active, leaving the U.S. with ARPA-E to fund, but not provide additional facilities, for the demonstration of new materials.

In contrast, Chinese companies investing in SiC and GaN technologies benefit from government support for the infrastructure required to bring such products to market, helping the PRC catch up to foreign leaders in substrate technology. By incorporating novel substrate technologies into its full-stack research projects, the NSTC could help provide testing grounds for startups otherwise unable to get such opportunities from industry.

Regarding new chemicals, the World Semiconductor Council (a global gathering of regional semiconductor industry associations) annually reminds regulators that certain toxic substances are currently irreplaceable for the chip making process. Per-and polyfluoroalkyl substances (PFAS) compounds are ubiquitous in fabs, but the industry has only succeeded in fully eliminating one particular PFAS compound (perfluorooctane sulfonic acid) since 2000 and has only committed to eliminating another (perfluorooctanoic acid) by 2025. Though the technical challenges of finding alternative chemicals and transitioning process steps are formidable, one industry observer laments that chip makers are dragging their feet due to their belief that regulators will continue allowing them to use PFAS. Making PFAS alternatives a research priority for the NSTC could catalyze such chemicals’ discovery and implementation while regulators still allow their limited use in chip production.

As with new materials, the semiconductor researchers lack testing grounds for potential PFAS alternative chemicals. The University of Arizona Engineering Research Center (ERC) for Environmentally Benign Semiconductor Manufacturing, an NSF-SRC program receiving approximately $1 million in initial annual public funding since 1997, has not been active since its last NSF grant ended in 2017. Additionally, the University of California Los Angeles (UCLA) Center for the Environmental Implications of Nanotechnology (CEIN) received approximately $6 million in initial public funding from the NSF and EPA from 2008 to 2013, and NSF extended this funding through 2017. However, CEIN primarily focuses on measuring the chip industry’s environmental impact, not on developing alternatives to hazardous chemicals.

New materials and new chemicals would confer benefits across the semiconductor industry and the larger U.S. technology ecosystem. This broad benefit, however, has to-date limited industry investment. The NSTC should not only invest in these new paradigms, but it should also fashion itself into a testing ground for the materials and chemicals that industry facilities will not risk trying. Doing so will define the NSTC’s physical infrastructure as a public good that helps solve some of chipmakers’ most consequential free-rider dilemmas.

Cross-sectoral missions

Cross-sectoral missions are research initiatives requiring participation from companies that usually pursue their own siloed research agendas. Rather than following corporate research agendas driven by firms’ quarterly financial cycles, these missions should be oriented toward downstream use cases in the public interest like machine learning, security, and sustainability. A financially viable NSTC could help coordinate chip technology developments needed for these downstream trends.

A research agenda targeting cross-sectoral missions would be different in kind from the Decadal Plan for Semiconductors, a research agenda laid out by industry players through the Semiconductor Industry Association (SIA) and the Semiconductor Research Corporation (SRC). The Decadal Plan delineates five categories of breakthroughs in memory, analog, communications, security, and sustainability. The first three categories of this plan are important and largely align with the research agendas of well-established chipmakers and designers, but the latter two categories convey the priorities of actors outside the core industry.

The NSTC, however, should draw inspiration from the Decadal Plan’s latter two categories, security and sustainability, to deliver the chip technology needed for world-changing downstream uses of advanced computation. The following are three examples of use-case driven research agendas:

Risky AI hardware bets

“The Hardware Lottery” describes how a research direction can win not because it’s necessarily the most promising, but because it’s the most well-suited to the capabilities of the underlying computer hardware. Nowhere is this more evident than when looking back from the current AI boom. The fundamental software ingredients for AI computing, namely neural networks and backpropagation, were developed many decades ago. But their promise wasn’t realized until GPUs were applied to the problem – a fortunate spillover from hardware developed for the gaming industry.

Unfortunately, no single hardware paradigm works ideally for every software paradigm, and the current approach to AI hardware also has its limitations. For example, Bayesian deep learning is regarded by many researchers as a promising approach, but has high computational costs and is difficult to parallelize over multiple GPUs.

Today’s AI hardware paradigm suffers from performance bottlenecks due to poor data movement: advances in how quickly chips can crunch numbers are far outpacing improvements in bandwidth and latency.

As companies race to specialize within the current AI hardware/software paradigm, the NSTC could support higher-risk work to explore the next paradigm. Beyond potentially leading to breakthroughs in areas such as optical computing and in-memory computing, risky hardware bets could allow software startups whose ideas do not fit into the current paradigm to achieve proof-of-concept.

System-level security

“Heterogeneous integration” (HI) has become chipmakers’ greatest hope to advance computing beyond the limits of Moore’s Law. At the same time, however, HI also makes chips more complicated, introducing more weak points that bad actors can exploit to hack devices. Importantly, no single developer has insight into all the potential security risks on a single heterogeneously integrated chip because siloed actors individually develop many of the final product’s “chiplet” subparts.

One key area of concern is advanced AI development, which often relies on highly complex GPU-based systems, and where IP presents an especially juicy target for well-resourced hackers. Independent researchers recently discovered a vulnerability in chips from four major GPU vendors that allowed adversaries to spy on outputs from other users’ LLM conversation sessions. The White House highlighted similar concerns in a report calling for chips of sensitive systems to deeply embed memory protections.

As chip development becomes more siloed due to HI, the NSTC could coordinate its members to identify and standardize solutions to system-level vulnerabilities. Specifically, it could help industry and academia jointly unravel structural problems in software and hardware stacks to ensure chip security is not solely dependent on individual companies’ foresight and due diligence. As we will elaborate in later sections, the NSTC could then use its role as a publicly subsidized consortium to make IP that is relevant to chip security as widely and cheaply available as possible.

PFAS in chip fabrication

Even before chips begin sucking power in massive data centers or on laptops, semiconductor fabs rely on electricity, water, and chemicals to run machines etching the designs on paper-thin sheets of silicon. The Decadal Plan envisions computing paradigms that could enable a more than million-fold improvement in operational efficiency. However, it omits any mention of sustainability in fabrication.

Creating and implementing safer process chemicals could be a prime area for the NSTC to gather chipmakers, toolmakers, chip designers, and upstream chemicals providers in pursuit of a stubborn challenge faced across chip segments and manufacturing steps. While the theorized causality between PFAS chemicals and harm to the human endocrine system has not been definitively proven, chipmakers have nonetheless faced increasingly tighter restrictions on PFAS use, as well as heavy pressure for a blanket ban on PFAS use by environmental advocates. The semiconductor industry has to-date been successful in delaying such bans by arguing that, without PFAS, chipmaking would grind to a halt in America. However, the U.S. Environmental Protection Agency’s 2023 proposition of complete ban suggests there may soon be a day when U.S. chipmakers have to entirely remove PFAS from their manufacturing processes, regardless of definitive scientific evidence.

As mentioned previously, alternatives to PFAS compounds have evaded the industry for over two decades. For individual companies to make breakthroughs in this field is challenging, because a) developing PFAS alternatives is undeniably hard and so requires expensive, risky upfront research, b) implementing PFAS alternatives would require significant manufacturing and design process changes, and c) the benefits would accrue to all industry actors and society more broadly (in the form of more sustainable fabrication). The NSTC should therefore organize cross-industry contributions to developing PFAS alternatives as a public good.

The NSTC’s leadership should identify overlap points between traditionally siloed technology verticals as early as possible. Once found, these overlaps should form the nexuses of the consortium’s research agenda, as opposed to planning it around analog, memory, logic, and other verticals that function as the industry existing foci. Such cross-sectoral orientation will make the NSTC a unique gathering spot for players across the industry to plan breakthrough goals.

Stay tuned for tomorrow for part 2, or just check out the Institute for Progress for the full report!

Thank you to Joe Pasetti, Travis Mosier, Daniel Armbrust, Todd Younkin, Dan Patt, John Cole, Yan Zheng, Eileen Tanghal, David Henshall, Sam Folk, Gary Ignatin, and others…